Überschrift und Einstieg

Intel versucht sein Comeback an einer unerwarteten Front: nicht beim kleinsten Transistor, sondern bei der Frage, wie mehrere Chips zu einem leistungsfähigen System verpackt werden. Was früher als nachgelagerter, wenig glamouröser Schritt galt, wird im Zeitalter der KI zum strategischen Hebel. Gelingt Intels Wette auf „Advanced Packaging“, kann der Konzern wieder eine zentrale Rolle spielen, ohne TSMC sofort bei 3‑nm‑ oder 2‑nm‑Technologie einzuholen. Misslingt sie, droht ein weiterer teurer Umweg in einer ohnehin turbulenten Unternehmensgeschichte. Dieser Artikel ordnet Intels Schritte ein und beleuchtet insbesondere die Konsequenzen für Europa und die DACH‑Region.

Die Nachricht in Kürze

Laut einem Bericht von Wired, der auf Ars Technica erschienen ist, investiert Intel Milliarden US‑Dollar in fortgeschrittene Verpackungstechnologien. Herzstück ist der Standort Rio Rancho im US‑Bundesstaat New Mexico, wo ein jahrelang stillgelegtes Werk (Fab 9) 2024 mithilfe von Geldern aus dem US‑CHIPS‑Act reaktiviert wurde. Gemeinsam mit der benachbarten Fab 11X bildet es nun das Zentrum von Intels Packaging‑Aktivitäten.

Diese Aktivitäten sind im Bereich Intel Foundry angesiedelt, also in der ausgelagerten Auftragsfertigung, die vom klassischen Prozessorproduktgeschäft organisatorisch getrennt wurde. Das Management erwartet laut Wired, dass die Verpackungserlöse die Marke von einer Milliarde US‑Dollar überschreiten und früher anlaufen als nennenswerte Waferumsätze der Foundry. Intel soll mit großen Cloudanbietern – namentlich Google und Amazon – über die Nutzung seiner Packaging‑Services für deren eigene KI‑Chips verhandeln. Parallel baut der Konzern in Penang (Malaysia) zusätzliche Kapazitäten für Montage, Test und Advanced Packaging auf und setzt dabei auf Technologien wie EMIB, Foveros und das neue EMIB‑T.

Warum das wichtig ist

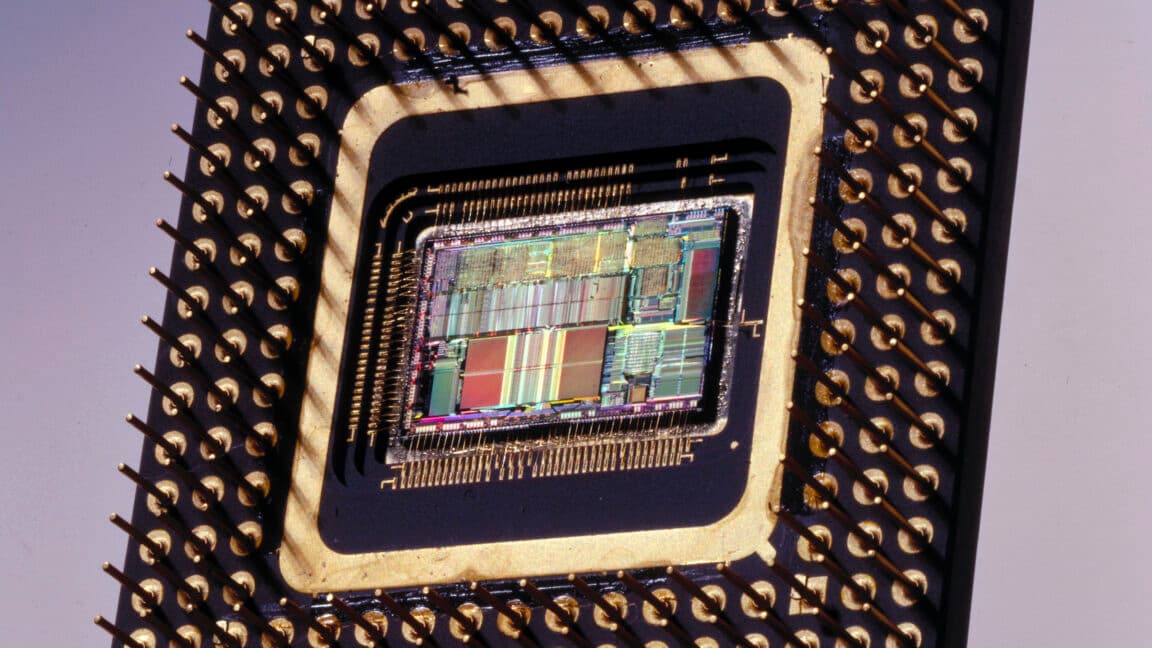

Die Halbleiterbranche lebte lange vom Dogma: „Kleiner ist besser.“ Doch im KI‑Zeitalter verlagert sich die Engstelle. Entscheidend ist nicht mehr nur, wie fein eine einzelne Logik‑ oder Speicherstruktur ist, sondern wie mehrere Dies, HBM‑Stacks und Interconnects im Paket zusammenarbeiten. Genau dort positioniert sich Intel.

Welche Dynamik entsteht, wenn Intel diese Wette gewinnt?

Abkürzung zurück in die Spitzengruppe. Intel kämpft seit Jahren damit, TSMC und Samsung bei den modernsten Fertigungsknoten einzuholen. Mit Advanced Packaging umgeht der Konzern dieses Wettrennen teilweise: Er kann Dies aus unterschiedlichen Quellen und Prozessgenerationen eng koppeln und so Mehrwert schaffen, ohne selbst überall technologischer Spitzenreiter zu sein.

Mehr Verhandlungsmacht für Hyperscaler. Google, Amazon & Co. entwickeln längst eigene KI‑Beschleuniger. Wenn sie die Frontend‑Fertigung bei einem Anbieter und das High‑End‑Packaging bei einem anderen einkaufen können, sind sie weniger vom „Alles aus einer Hand“-Modell TSMC abhängig. Allein die Option, zu Intel zu gehen, stärkt ihre Verhandlungsposition.

Attraktive Margen in einem neuen Profitcenter. Intels Finanzchef peilt Bruttomargen von rund 40 Prozent im Packaging‑Geschäft an – ähnlich wie im klassischen CPU‑Segment. Angesichts der Knappheit an High‑End‑Packaging für KI‑Chips ist das realistisch.

Druck auf traditionelle OSAT‑Dienstleister. Firmen wie ASE oder Amkor dominierten bisher das Outsourcing von Assembly und Test. Doch das High‑End‑Segment – 2,5D, 3D, HBM‑Intgration – wandert zunehmend zu den Foundries selbst. Wenn Intel hier ernsthaft mitmischt, dürfte am oberen Ende der Wertschöpfungskette wenig Platz für klassische OSATs bleiben.

Die Verlierer könnten zunächst kleinere Chipdesigner sein, die auf schnelle, standardisierte und günstige High‑End‑Verpackung gehofft hatten. Intels Plan setzt auf das Gegenteil: Advanced Packaging als knappen, hochmargigen Engpass.

Der größere Kontext

Intels Offensive passt nahtlos in mehrere Entwicklungslinien der letzten Jahre.

1. Chiplets und 3D‑Integration.

AMD hat mit seinen EPYC‑Serverprozessoren und den Ryzen‑CPUs gezeigt, wie man große Chips in mehrere kleinere Dies aufteilt, die über das Package verbunden werden. Apple verbindet zwei M1‑Max‑Dies zum M1 Ultra. Industrieinitiativen wie UCIe sollen künftig sogar das Kombinieren von Dies unterschiedlicher Hersteller ermöglichen.

Solche Konzepte skalieren nur, wenn Packaging‑Technologien sehr breite, latenzarme und energieeffiziente Verbindungen bereitstellen. TSMC ist mit CoWoS und SoIC hier Vorreiter; Nvidia ist darauf für seine KI‑GPUs stark angewiesen. Intel versucht mit EMIB, Foveros und nun EMIB‑T, eine gleichwertige – wenn nicht überlegene – Alternative anzubieten.

2. KI als Speicher‑ und Bandbreitenproblem.

Große neuronale Netze zu trainieren, ist weniger eine Frage einzelner FLOPS, sondern eine Frage, wie schnell Daten zwischen Recheneinheiten und HBM transportiert werden können. Die Engpässe bei Nvidias GPUs in den Jahren 2023/24 waren nicht nur eine Frage der Wafer‑Kapazität, sondern auch der begrenzten CoWoS‑Packaging‑Ressourcen bei TSMC. Wer Advanced Packaging kontrolliert, kontrolliert zunehmend die effektive KI‑Kapazität des Marktes.

3. Industriepolitik und Resilienz.

Frontend‑Fertigung ist heute stark in Taiwan und Südkorea konzentriert, Packaging überwiegend in Südostasien. Spätestens seit der Pandemie und der Taiwan‑Debatte ist klar, dass diese Konzentration ein Risiko darstellt. Der US‑CHIPS‑Act für Rio Rancho zielt genau darauf ab, kritische Teile der Wertschöpfung – inklusive Advanced Packaging – auf US‑Boden zu holen.

Für Europa heißt das: Wer nur auf klassische Fabs setzt, sich aber beim Packaging weiter auf Asien verlässt, baut eine halbe Souveränität auf. Die eigentlichen Flaschenhälse können andernorts bleiben.

Die europäische Perspektive (DACH inklusive)

Europa und die DACH‑Region stehen genau an diesem Scheideweg.

Die EU‑Chips‑Verordnung wird vor allem mit Großprojekten wie Intels geplantem Megawerk in Magdeburg, der TSMC‑Ansiedlung in Dresden und Ausbauplänen von STMicroelectronics oder Infineon verbunden. Weniger im Rampenlicht steht die Frage: Wo werden die resultierenden Dies eigentlich hochwertig verpackt?

Aktuell verlassen sich europäische Chipentwickler und ‑nutzer stark auf Packaging‑Kapazitäten in Asien. Intels Schritt zeigt, dass gerade im KI‑Segment ein großer Teil der Wertschöpfung – und der Kontrolle über Systemleistung – in diese Ebene wandert.

Europa bringt jedoch einige Trümpfe mit:

- Forschungsinstitute wie imec (Belgien) oder das Fraunhofer‑Netzwerk (Deutschland) forschen seit Jahren an 2,5D‑ und 3D‑Integration.

- Intel ist mit seinem Standort in Irland bereits stark präsent und hat in der Vergangenheit über ein Assembly‑ und Packaging‑Werk in Italien verhandelt.

- Der deutschsprachige Raum verfügt mit Playern wie Infineon, Bosch und zahlreichen Hidden Champions im Maschinenbau über eine Basis, um etwa Equipment, Materialien und Testtechnologien für Advanced Packaging zu liefern.

Für deutsche Unternehmen kommt ein weiterer Aspekt hinzu: Datenschutz und Energieeffizienz. Hochintegrierte KI‑Chips mit besserem Packaging können Rechenzentren effizienter machen – ein Pluspunkt sowohl für die Stromrechnung als auch für ESG‑Berichte und die Akzeptanz neuer Rechenzentren in der Öffentlichkeit.

Cloud‑Anbieter aus der Region (z. B. Deutsche Telekom, IONOS, Swisscom) könnten mittelbar profitieren, wenn Google oder Amazon dank neuer Packaging‑Optionen günstigere oder effizientere KI‑Ressourcen in ihren europäischen Regionen anbieten. Gleichzeitig bleibt die Frage, ob Europa selbst eine nennenswerte High‑End‑Packaging‑Kapazität aufbauen wird – oder sich dauerhaft auf US‑ und asiatische Anbieter verlässt.

Ausblick

Die kommenden zwei bis drei Jahre werden zeigen, ob Advanced Packaging wirklich zum „interessantesten Teil des Foundry‑Geschäfts“ wird, wie es Intel intern formuliert.

Worauf sollten Beobachter achten?

Konkrete Referenzkunden. Sobald Google, Amazon oder ein anderer Hyperscaler öffentlich bestätigt, Intel für Packaging zu nutzen, ist das ein starkes Signal – sowohl an Investoren als auch an TSMC.

Kapazitätsausbau und Capex. Intel selbst sagt, dass steigende Investitionsausgaben im Packaging ein Indikator dafür sein werden, dass größere Kundenverträge unterschrieben sind. Wer die Quartalsberichte liest, wird das schnell sehen.

Technische Reife. EMIB‑T und andere Technologien müssen nicht nur funktionieren, sondern reproduzierbar mit hohen Ausbeuten laufen. Gerade hier war Intel in der Vergangenheit immer wieder ins Stolpern geraten.

Reaktion der Politik. In den USA wie in Europa dürften Advanced‑Packaging‑Kapazitäten zunehmend als sicherheitsrelevant eingestuft werden. Exportkontrollen, Subventionen oder auch Auflagen (z. B. im Rahmen des EU‑Chips‑Acts) könnten konkret auf diesen Bereich zielen.

Für Unternehmen in der DACH‑Region ergeben sich zwei Chancen: Erstens, als Kunden von mehr Wettbewerb zwischen TSMC und Intel zu profitieren – etwa bei kundenspezifischen KI‑Beschleunigern. Zweitens, als Zulieferer oder Partner für Equipment, Materialien, Simulation und Test im Advanced‑Packaging‑Ökosystem Fuß zu fassen.

Fazit

Intels Offensive im Bereich Advanced Packaging ist wahrscheinlich der realistischste Hebel, den der Konzern aktuell hat, um im KI‑Zeitalter wieder Relevanz zu gewinnen. Sie adressiert einen echten Engpass, stützt sich auf staatliche Förderung und trifft einen Markt mit enormer Nachfrage. Aber sie ist auch riskant: technisch anspruchsvoll, kapitalintensiv und eingebettet in ein geopolitisch sensibles Umfeld. Für Europa und die DACH‑Region lautet die Kernfrage: Wollen wir bei dieser neuen Schlüsselschicht der Wertschöpfung nur zusehen – oder sie aktiv mitgestalten?